## WINFORD ENGINEERING, LLC

4561 Garfield Road • Auburn. MI 48611

Phone: 1-877-634-2673 FAX: 1-989-671-2941 www.winford.com

#### **OPI104-HS Datasheet**

Product Revision: Rev A

# OP1104 Roths Story A Company Roths Story Roths R

OPI104-HS-FT shown

#### Overview

The OPI104-HS provides four channels of optical isolation with both a non-inverting output and an inverting output for each channel. Both the input side and the output side are designed to interface with equipment using logic voltages of anywhere from 3.3V to 24V. This -HS variant includes standard FET low-side outputs that provide significant sink current capability. While these standard FETs do not include over-current protection or over-temperature protection, they are significantly faster and are

rated for higher current than the protected FETs used on the standard (non -HS) OPI104 version. Reverse-polarity protection on inputs and outputs is also included. Terminal blocks provide easy access to the signals.

Note that on the output side, the pull-up voltage (VPU) and ground reference (GND) are common to all four channels. On the input-side, the four channels are completely independent.

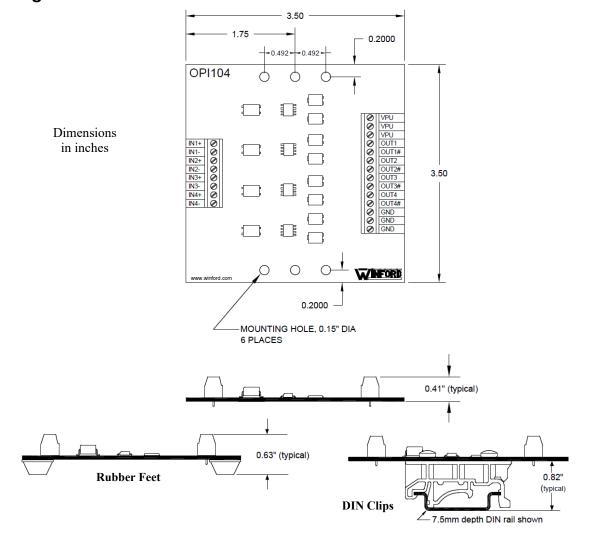

## **Drawing**

## **Part Number Ordering Information**

## 1. Mounting Option

- FT Rubber Feet on bottom side of PCB

- **DIN** DIN Rail Mounting Clips

#### **OPI104-HS Stocked Part Numbers**

The following part numbers represent standard options that are normally stocked:

- · OPI104-HS-FT

- OPI104-HS-DIN

Note: The following additional options utilize a protected output stage. See the OPI104 datasheet for details.

- OPI104-FT (protected output stage)

- OPI104-DIN (protected output stage)

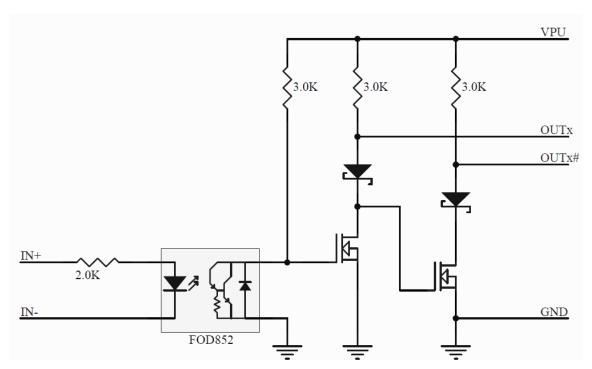

# **Simplified Schematic Drawing (one channel)**

Note that VPU and GND (output side) are common to all four channels.

# **Operating Conditions**

| Ambient Temperature Range                         | −30°C to 85°C |

|---------------------------------------------------|---------------|

| Relative Humidity Range - not icing or condensing | 5% to 85% RH  |

# **Absolute Maximum Ratings**

| Specification                                                                           | Symbol           | Min | Тур | Max                      | Unit        |

|-----------------------------------------------------------------------------------------|------------------|-----|-----|--------------------------|-------------|

| Input Signal Voltage (INx+ relative to INx-)                                            | INx              |     |     | 28                       | V           |

| Output Pull-Up Voltage (relative to GND)                                                | VPU              |     |     | 30                       | V           |

| Max rated sink current @ -30 degC<br>VPU = 3.3V<br>VPU = 5.0V<br>VPU = 12V<br>VPU = 24V | IOUTx,<br>IOUTx# |     |     | 4<br>6<br>6<br>6         | A<br>A<br>A |

| Max rated sink current @ 25 degC<br>VPU = 3.3V<br>VPU = 5.0V<br>VPU = 12V<br>VPU = 24V  | IOUTx,<br>IOUTx# |     |     | 2.7<br>4.5<br>4.5<br>4.5 | A<br>A<br>A |

| Max rated sink current @ 85 degC  VPU = 3.3V  VPU = 5.0V  VPU = 12V  VPU = 24V          | IOUTx,<br>IOUTx# |     |     | 1.5<br>2.8<br>2.8<br>2.8 | A<br>A<br>A |

| Max current for any terminal block position @ 25 degC                                   | ITB_25           |     |     | 10                       | A           |

| Max current for any terminal block position @ 85 degC                                   | ITB_85           |     |     | 8                        | A           |

# **Electrical Performance and Recommended Operating Conditions (at 25 degC)**

| Specification / Conditions                                   | Min | Тур | Max | Unit |

|--------------------------------------------------------------|-----|-----|-----|------|

| INx Input Voltage for guaranteed logic low                   | 0.0 |     | 0.8 | V    |

| INx Input Voltage for guaranteed logic high                  | 3.2 |     | 25  | V    |

| Typical INx logic switching threshold                        |     | 2.0 |     | V    |

| Input current, INx = 3.3V                                    |     | 1.0 |     | mA   |

| Input current, $INx = 5.0V$                                  |     | 2.0 |     | mA   |

| Input current, $INx = 12V$                                   |     | 5.3 |     | mA   |

| Input current, INx = 24V                                     |     | 11  |     | mA   |

| VPU (output-side pullup voltage) recommended operating range | 3.2 |     | 25  | V    |

| VPU supply current draw (no external loading)                |     | 15  | 20  | mA   |

| Specification / Conditions                                                                           | Min       | Тур          | Max          | Unit                                              |

|------------------------------------------------------------------------------------------------------|-----------|--------------|--------------|---------------------------------------------------|

| Non-inverting output OUTx Voltage, Low State (FET active) INx = Logic Low VPU = 3.3V                 |           |              |              |                                                   |

| RLOAD = 1.1 Ohms <sup>1</sup><br>RLOAD = not present                                                 |           | 0.45<br>0.15 | 0.55<br>0.30 | V<br>V                                            |

| Inverting output OUTx# Voltage, Low State (FET active) INx = Logic High VPU = 3.3V                   |           |              |              |                                                   |

| $RLOAD = 1.1 Ohms^{2}$ $RLOAD = not present$                                                         |           | 0.45<br>0.15 | 0.55<br>0.30 | V<br>V                                            |

| Non-inverting output OUTx Voltage, Low State (FET active) INx = Logic Low VPU = 5.0V                 |           |              |              |                                                   |

| RLOAD = 1.1 Ohms <sup>1</sup><br>RLOAD = not present                                                 |           | 0.50<br>0.15 | 0.65<br>0.30 | $\left  egin{array}{c} V \ V \end{array} \right $ |

| Inverting output OUTx# Voltage, Low State (FET active) INx = Logic High VPU = 5.0V                   |           |              |              |                                                   |

| $RLOAD = 1.1 \text{ Ohms}^2$ $RLOAD = \text{not present}$                                            |           | 0.50<br>0.15 | 0.65<br>0.30 | V<br>V                                            |

| Non-inverting output OUTx Voltage, Low State (FET active) INx = Logic Low VPU = 12.0V                |           |              |              | V                                                 |

| RLOAD = 2.7 Ohms <sup>1</sup><br>RLOAD = not present                                                 |           | 0.50<br>0.15 | 0.65<br>0.30 |                                                   |

| Inverting output OUTx# Voltage, Low State (FET active) INx = Logic High VPU = 12.0V                  |           |              |              | V                                                 |

| $RLOAD = 2.7 \text{ Ohms}^2$ $RLOAD = \text{not present}$                                            |           | 0.50<br>0.15 | 0.65<br>0.30 |                                                   |

| Non-inverting output OUTx Voltage, Low State (FET active) INx = Logic Low VPU = 24.0V                |           |              |              | V                                                 |

| RLOAD = 5.4 Ohms <sup>1</sup><br>RLOAD = not present                                                 |           | 0.50<br>0.15 | 0.65<br>0.30 |                                                   |

| Inverting output OUTx# Voltage, Low State (FET active) INx = Logic High VPU = 24.0V                  |           |              |              | V                                                 |

| $RLOAD = 5.4 \text{ Ohms}^2$ $RLOAD = \text{not present}$                                            |           | 0.50<br>0.15 | 0.65<br>0.30 |                                                   |

| Non-inverting output OUTx Voltage, High State INx = Logic High VPU = 3.2V to 25V No external loading | VPU – 0.3 |              |              | V                                                 |

| Specification / Conditions                                                                          | Min       | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------------|-----------|-----|-----|------|

| Inverting output OUTx# Voltage, High State  INx = Logic Low  VPU = 3.2V to 25V  No external loading | VPU – 0.3 |     |     | V    |

# **Optocoupler Isolation Performance\***

| Specification                                                                         | Symbol     | Value | Unit              |

|---------------------------------------------------------------------------------------|------------|-------|-------------------|

| Maximum Working Insulation Voltage (continuous) (assumes no contamination on the PCB) | $V_{IORM}$ | 850   | $V_{ m peak}$     |

| Highest Allowable Over-voltage (transient) (assumes no contamination on the PCB)      | $V_{IOTM}$ | 6000  | V <sub>peak</sub> |

<sup>\*</sup>Refer to the optocoupler datasheet for additional information. Optocoupler manufacturer and part number are listed in the Component Details section of this document.

## **Screw Terminal Wire Sizes**

• All Signals and Power: 16-26 AWG

# **Component Details**

| Component                                  | Manufacturer     | Manuf. Part Number |

|--------------------------------------------|------------------|--------------------|

| Optocoupler                                | ON Semiconductor | FOD852             |

| Input Resistor                             | (any)            | 2.0 kΩ             |

| Output Pull-up Resistor                    | (any)            | 3.0 kΩ             |

| Output Low-Side Driver, Dual MOSFET        | Vishay           | Si4804CDY          |

| Output Diode (reverse-polarity protection) | Nexperia         | PMEG045V100EPD     |

RLOAD placed between VPU supply and output OUTx. See applications section for details.

RLOAD placed between VPU supply and output OUTx#. See applications section for details.

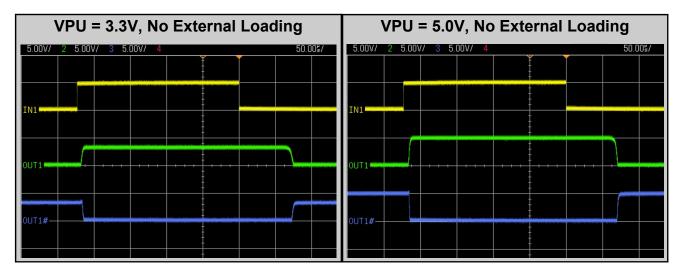

# **Timing Performance**

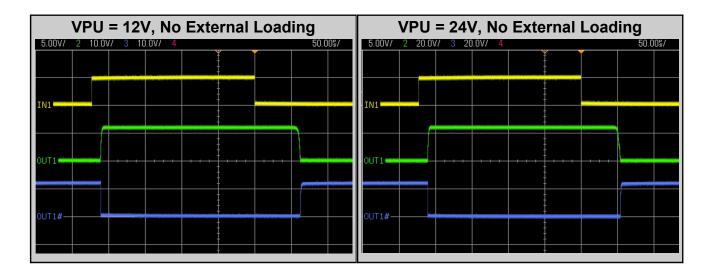

Typical signal timing is provided below (for a single channel). All plots below use a time scale of  $50 \mu s$  (microseconds) per division:

# Applications (OPI104 and OPI104-HS)

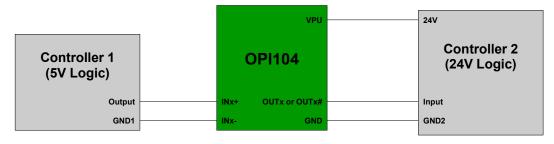

This product allows a digital signal to be sent from one circuit to another while maintaining isolation between the two circuits. This is useful when the two circuits are operating at different ground potentials by design, as well as the case in which there may be a ground shift between the two circuits due to a common-impedance condition in which the ground line is shared with a high-current load. In addition, this product provides a method to perform logic level translation since it allows the two circuits to use different logic voltages.

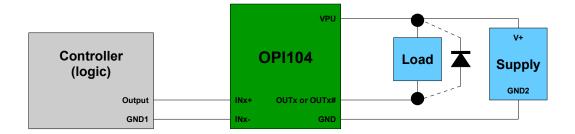

This product is also suitable for use as an isolated low-side driver for a small DC motor, solenoid, relay coil, bulb, or similar. For this type of application in which the low-side output driver sinks additional current beyond the current flowing thru the output pull-up resistor, the user should note the electrical performance characteristics table in which max rated sink current is specified for various conditions. It is also advisable to include external clamping for inductive loads (e.g., diode placed across the load, as shown below).

This product provides both a non-inverting output and an inverting output on each channel. Note that both outputs (non-inverting and inverting) are open-drain outputs. That is, each of the outputs is able to sink a significant amount of current, but can only source current thru its output pull-up resistor.

If there are additional questions about using this product in a particular application, please contact Winford Engineering for more information.

## Changes

| Date       | Description                                                                                |

|------------|--------------------------------------------------------------------------------------------|

| 06/22/2022 | Initial release for OPI104-HS                                                              |

| 01/27/2023 | Clarified scope plot time scale                                                            |

| 06/08/2023 | Added clarification indicating that VPU and GND are common to all 4 channels (output side) |

#### **Notices**

- 1. Drawings and specifications are subject to change without notice.

- 2. Winford Engineering, LLC does not authorize any of its products for use in military, medical or other life-critical systems and/or devices. Life-critical devices/systems include devices or systems which, a) are intended for surgical implantation into the body, or b) support or sustain life and whose failure to perform can be reasonably expected to result in injury. Winford Engineering, LLC products are not designed with the components required, and are not subject to the testing required to ensure a level of reliability suitable for the treatment and diagnosis of people. Winford Engineering, LLC shall not be held responsible or liable for damages or injury that occur as a result of the use of this product.